# DISEÑO ASISTIDO POR COMPUTADORA PARA LA ENSEÑANZA DE SISTEMAS DIGITALES

C. F. Hernández Farfán<sup>1</sup>

D. A. Álvarez Medina<sup>2</sup>

M. Arroyo Almaguer<sup>3</sup>

#### RESUMEN

Las técnicas de diseño asistido por computadora se emplean en diferentes campos de la ingeniería, representan una herramienta indispensable para los ingenieros en el ejercicio de su profesión. Sin embargo, el acceso a éstas técnicas de diseño por parte de los estudiantes de ingeniería no siempre es de gran cobertura, con el objetivo de ampliar esta cobertura en el campo del diseño de sistemas digitales como parte de la formación de los estudiantes de ingeniería en sistemas computacionales, en este trabajo se muestra la técnica de diseño asistido por computadora para la implementación de sistemas digitales y el grado de aceptación o adaptación a un determinado curso de la carrera. En este proyecto se presenta la forma de emplear el software de diseño asistido por computadora Quartus II v 12.0 Web Edition y la tarjeta de desarrollo basada en FPGA Cyclone II ambos productos tecnológicos desarrollados por la compañía Altera Corporation. Se describe cada sistema digital por medio del lenguaje VHDL, se compila y se simula para su realización física en la tarjeta de desarrollo. Se trabajó con estudiantes y profesores del Instituto Tecnológico Superior de Irapuato para la prueba y realización de sistemas digitales. El grado de aceptación del uso de estas herramientas para el aprendizaje por parte de los estudiantes es bastante bueno. Se puede observar que el uso de la capacidad de la tarjeta es menor del 1 %, por lo que se propone buscar aplicaciones más robustas.

#### **ANTECEDENTES**

Actualmente los proyectos en los diferentes campos de la ingeniería están basados en herramientas de diseño asistido por computadora (CAD, por sus siglas en inglés). Debido a las diversas aplicaciones especificas de la electrónica digital y a la necesidad de llevar a cabo el proceso de diseño de una forma más eficiente se desarrollaron herramientas de diseño asistido por computadora y el empleo de circuitos digitales casi a la medida de cada necesidad.

El proceso de diseño de sistemas digitales se ha hecho más eficiente, reduciendo costos de producción, facilitando modificaciones al proyecto, reducción de espacio físico y proporcionando soluciones a la medida, gracias al el empleo del software de diseño asistido por computadora y uso de dispositivos lógicos programables de alta capacidad y desempeño. "Existe una gran variedad de dispositivos lógicos programables, los cuales se usan para reemplazar circuitos de pequeña, mediana y muy alta escala de integración, ya que ahorran espacio y reducen el costo de los diseños" (Maxinez & Alcalá, 2002). Dentro de los dispositivos lógicos programables se encuentran los dispositivos denominados FPGA, arreglos de compuertas programables en campo. Son considerados de mayor capacidad en diferentes sentidos y se emplearan en este proyecto, no por la capacidad requerida para el proyecto sino por su disponibilidad, para familiarizarse con su manejo y posteriormente iniciar su empleo aprovechando todas sus capacidades en la solución de problemas de cómputo científico.

\_

<sup>&</sup>lt;sup>1</sup> Profesor. Instituto Tecnológico Superior de <u>Irapuato.cahernandez@itesi.edu.mx</u>.

<sup>&</sup>lt;sup>2</sup> Profesora del Instituto Tecnológico Superior de <u>Irapuato.doalvarez@itesi.edu.mx</u>.

<sup>&</sup>lt;sup>3</sup> Profesora del Instituto Tecnológico Superior de Irapuato. maarroyo@itesi.edu.mx.

La técnica CAD de sistemas digitales requiere de la descripción del sistema digital por medio de un lenguaje de programación, que sea poderoso, muy difundido y estandarizado, dicho lenguaje es VHDL (VHSIC Hardware Description Language) que se adapta a la mayoría de los requerimientos de los sistemas digitales, a los diferentes fabricantes de software de diseño y la mayoría de los dispositivos programables. "La programación en VHDL cuenta con una notación que permite su uso en cualquier diseño electrónico. VHDL es un estándar no sometido a patente o marca registrada por lo que se puede utilizar sin restricciones, IEEE lo mantiene y documenta por lo que existe garantía de estabilidad y soporte." (Maxinez & Alcalá, 2002)

"El software CAD facilita implementar un sistema digital especifico, usando un dispositivo programable como FPGA" (Altera Corporation, 2006). El proceso de diseño consiste en la descripción del sistema digital por medio de código VHDL, la síntesis para establecer las interconexiones necesarias dentro del dispositivo FPGA, una simulación para determinar el correcto funcionamiento del circuito, la ubicación de los elementos lógicos, análisis del desempeño en el tiempo, y la programación o realización física del circuito en una tarjeta.

Dentro del plan de estudios de la Dirección General de Educación Superior Tecnológica para los Institutos Tecnológicos en la carrera de Ingeniería en Sistemas Computacionales se imparten las materias del área de electrónica digital como Principios Eléctricos y Aplicaciones Digitales, Arquitectura de Computadoras y Sistemas Programables; las cuales aportan al perfil de egreso las competencias que les permitan a los estudiantes diseñar soluciones tecnológicas en las que se involucren el diseño de sistemas digitales y la interacción hombre-máquina. Sin embargo se debe considerar que el proceso de diseño empleando herramientas CAD no siempre es de gran cobertura, que el proceso de enseñanza tiene la necesidad hacer un balance entre los conceptos teóricos y su implementación física, además la implementación de sistemas digitales basada en el empleo de circuitos integrados de mediana escala de integración es sumamente complicada, requiere bastante tiempo de desarrollo e implica el costo de adquirir los componentes individuales del proyecto así como recursos adicionales de laboratorio. Pero por otra parte se cuenta relativa facilidad de acceso al software de diseño y a la tarjeta de desarrollo.

Debido a esto se plantea el objetivo de este trabajo que consiste en mostrar el uso del software de diseño asistido por computadora Quartus II Web Edition y la tarjeta de desarrollo de sistemas digitales basada en FPGA denominada Cyclone II mediante la implementación de sistemas digitales para las materias de Principios Eléctricos y Aplicaciones Digitales, Arquitectura de Computadoras y Sistemas Programables de la carrera de Ingeniería en Sistemas Computacionales en el Instituto Tecnológico Superior de Irapuato (ITESI).

### **METODOLOGÍA**

En este proyecto se trabaja con la hipótesis de que mediante el uso de herramientas CAD computadora se pueden describir los componentes digitales que se incluyen en el programa de estudios de la carrera de Ing. Sistemas Computacionales en las materias de Principios Eléctricos y Aplicaciones Digitales, Arquitectura de Computadoras y Sistemas Programables; que es viable su uso y que se pueden proponer aplicaciones más robustas como cómputo de alto desempeño.

El uso de herramientas CAD de sistemas digitales para este proyecto requiere de un soporte básico formado por una computadora personal, en este caso con características bastante comunes y de coste bajo. Por ejemplo una computadora con procesador Intel Premium Dual Core a 1.86 Ghz, 2 GB de memoria Ram, 160 GB de capacidad de disco duro y sistema operativo Windows Vista. Existen diversas compañías de soporte de hardware y software que ofrecen una gran variedad de productos de alto desempeño para casi cualquier aplicación como Altera Corporation, Cypress Semiconductor, Xilinx, etc. Debido a la disponibilidad de software y hardware con la que actualmente se cuenta en el instituto, se emplea el software de diseño asistido por computadora Quartus II v 12.0 Web Edition y la tarjeta de desarrollo basada en FPGA Cyclone II, ambos productos tecnológicos desarrollados por la compañía Altera Corporation.

Se realiza el proceso de diseño de lógica digital tal como compuertas lógicas, elementos de memoria o flip-flops, circuitos combinatorios como sumadores, comparadores y circuitos secuenciales como maquinas de estados y contadores digitales; componentes digitales tales como decodificadores, codificadores, multiplexores, registros y memorias; transferencias entre registros a través de un sistema de comunicación de datos o bus, unidades aritméticas y lógicas para la realización de microoperaciones, así como la descripción de una computadora básica y diseño de controladores.

Para cada descripción de hardware por medio del lenguaje, se revisa su correcta compilación, el análisis y síntesis debe completarse al 100%, la etapa de ubicación y utilización de los elementos lógicos de la tarjeta que implementan el diseño se deben completar igualmente al 100% así como la generación de archivos para la programación o realización del diseño en la tarjeta. La etapa de simulación se realizará en modo funcional debe comprobar las diferentes condiciones de las variables de entrada al circuito en particular y verificarse que la salida es tal como se desea en el comportamiento del circuito. Para la realización de pruebas se emplean entradas manuales por medio de interruptores y se visualizan las variables de salida a través de led's de la tarjeta.

Cada diseño básico es probado por un grupo de estudiantes para determinar el correcto funcionamiento de los circuitos digitales. Se realiza una encuesta a los estudiantes para determinar el grado de comprensión de ésta técnica y posibles dificultades pueden pudieran presentar.

Considerando que se trata de un proceso de diseño didáctico se emplea solo una librería estándar para construir todos los bloques funcionales así mismo se evita posibles problemas de compatibilidad entre diferentes fabricantes. Se inicia con la descripción de componentes básicos los cuales a su vez conforman componentes digitales más complejos capaces de realizar alguna determinada tarea y posteriormente éstos bloques son empleados en la construcción de sistemas digitales.

## Ejemplo de diseño

En este ejemplo se muestra el proceso de interconexión de los componentes de una computadora básica basada en la organización y diseño básico de computadoras de Morris Mano. "Aunque la computadora básica que se presenta es muy pequeña en comparación con las computadoras comerciales, tiene la ventaja de ser la suficientemente simple para

mostrar el proceso de diseño sin demasiadas complicaciones" (Mano, 1994). Para las pruebas iniciales, la computadora básica tiene un sistema de bus para datos y direcciones de 4 bits, 8 registros de 4 bits, una memoria ram y una unidad lógica aritmética. Una vez probada éstas capacidades se pueden ampliar mediante modificaciones al código en VHDL.

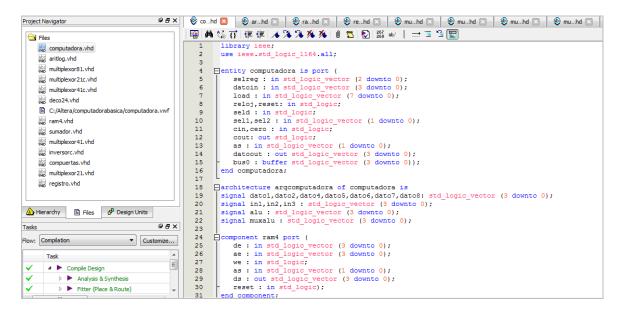

"El diseño jerárquico es el proceso de planeación en el desarrollo de un circuito mediante su distribución en bloques funcionales. El diseño top-down establece una jerarquía superior donde se parte del concepto y se van desarrollando los módulos de menor nivel hasta completar el sistema cuando se llega al nivel inferior. La solución comienza siempre desde el nivel superior y se va fragmentando hasta sus bloques básicos. En un primer nivel se definen las terminales que debe tener el sistema completo, así como las interconexiones entre los bloques de segundo nivel." (Romero, 2007). Para la descripción de este ejemplo la técnica de diseño jerárquico tipo top-down. En la Figura 1 se muestra la descripción de nivel 1 ó general de la computadora básica. En la ventana de la parte derecha se muestra la parte del código donde se especifican las entradas, salidas y señales intermedias del sistema digital.

Figura 1. Entradas y salidas de computadora

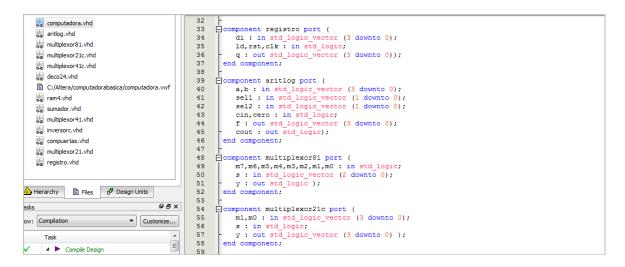

En la Figura 2 se muestra la declaración de componentes que integran el sistema tales como memoria ram, unidad aritmética y lógica, registros y multiplexores.

Figura 2. Componentes de la computadora

"VHDL permite ser usado como lenguaje de descripción de estructura, se ponen los componentes y sus interconexiones" (Pardo & Boluda, 1999). De esta manera en la Figura 3 se muestra la forma en que los componentes de la computadora básica se interconectan.

```

abd aritlog.vhd

u0: registro port map (bus0,load(0),reset,reloj,datoout);

u1: registro port map (bus0,load(1),reset,reloj,dato1);

u2: registro port map (bus0,load(2),reset,reloj,dato2);

u3: registro port map (bus0,load(3),reset,reloj,dato2);

u3: registro port map (alu,load(4),reset,reloj,dato4);

u5: registro port map (alu,load(4),reset,reloj,dato5);

u6: registro port map (bus0,load(6),reset,reloj,dato5);

u7: registro port map (bus0,load(6),reset,reloj,dato6);

u7: registro port map (bus0,load(7),reset,reloj,dato7);

u8: ramd port map (bus0,load(7),reset,reloj,dato7);

u9: aritloq port map (muxelu,in2,sel1,sel2,cin,cero,slu,cout);

u10: multiplexor81 port map (dato8(0),dato7(0),dato6(0),dato5(0),dato4(0),dato2(0),dato1(0),cero,selreg,bus0(0));

u11: multiplexor81 port map (dato8(1),dato7(1),dato6(1),dato5(1),dato4(2),dato2(2),dato1(2),cero,selreg,bus0(1));

u12: multiplexor81 port map (dato8(2),dato7(3),dato6(3),dato5(3),dato4(3),dato2(3),dato1(3),cero,selreg,bus0(3));

u13: multiplexor81 port map (dato8(3),dato7(3),dato6(3),dato5(3),dato4(3),dato2(3),dato1(3),cero,selreg,bus0(3));

u16: multiplexor81 port map (dato8(3),dato7(3),dato6(3),dato5(3),dato4(3),dato2(3),dato1(3),cero,selreg,bus0(3));

u16: multiplexor81 port map (dato8(3),dato7(3),dato6(3),dato5(3),dato4(3),dato2(3),dato1(3),cero,selreg,bus0(3));

u16: multiplexor81 port map (dato8(3),dato8(3),dato5(3),dato5(3),dato2(3),dato1(3),cero,selreg,bus0(3));

u16: multiplexor81 port map (dato8(3),dato8(3),dato8(3),dato5(3),dato2(3),dato1(3),cero,selreg,bus0(3));

u16: multiplexor81 port map (dato8(3),dato8(3),dato8(3),dato8(3),dato2(3),dato1(3),cero,selreg,bus0(3));

u16: multiplexor81 port map (dato8(3),dato8(3),dato8(3),dato8(3),dato2(3),dato1(3),cero,selreg,bus0(3));

u16: multiplexor81 port map (dato8(3),dato8(3),dato8(3),dato8(3),dato1(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),dato8(3),d

u0: registro port map (bus0,load(0),reset,reloj,datoout);

abd multiplexor81.vhd

hbd multiplexor21c.vhd

multiplexor41c.vhd

abd deco24.vhd

C:/Altera/com

abd ram4.vhd

sumador.vhd

multiplexor41.vhd

abd inversorc.vhd

abd compuertas.vhd

multiplexor21.vhd

abo registro.vhd

end argcomputadora;

```

Figura 3. Interconexión de componentes de la computadora

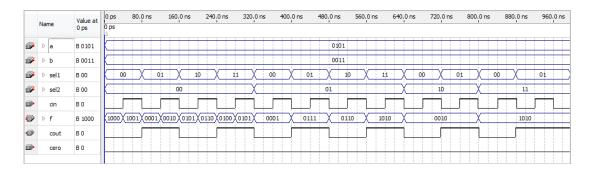

En la parte izquierda de la Figura 1 pueden notarse los componentes que integran la computadora, los cuales cada uno se encuentra descrito en un archivo aparte que puede ser compilado, probado y posteriormente integrado al proyecto. De estos componentes de la computadora básica, tanto la unidad aritmética y lógica, así como la memoria ram requieren ser descritos en base a los componentes que los integran, es decir realizar una descripción de nivel 2. En la Figura 4 se muestra simulación de la operación de la unidad aritmetica, lógica y de corrimiento. Finalmente en el código de nivel 3 jerárquico se describe cada componente individual del cual esta conformada la arquitectura, por ejemplo se describen multiplexores, registros, decodificadores, sumadores y compuertas lógicas. En la Figura 5 se muestra el ejemplo de la descripción en VHDL de un multiplexor de 4 a 1 cuadruple.

Figura 4. Operaciones unidad aritmética-lógica

```

library ieee;

use ieee.std logic 1164.all;

entity multiplexor41c is port (

e0,e1,e2,e3 : in std_logic_vector (3 downto 0);

s : in std_logic_vector (1 downto 0);

y : out std_logic_vector (3 downto 0));

end multiplexor41c;

architecture arqmultiplexor41c of multiplexor41c is

begin

process (s,e0,e1,e2,e3)

begin

case s is

when "00" => y <= e0;

when "01" => y <= e1;

when "10" => y <= e2;

when others => y <= e3;

end case;

end process:

end arqmultiplexor41c;

```

Figura 5. Multiplexor 4 a 1 cuádruple

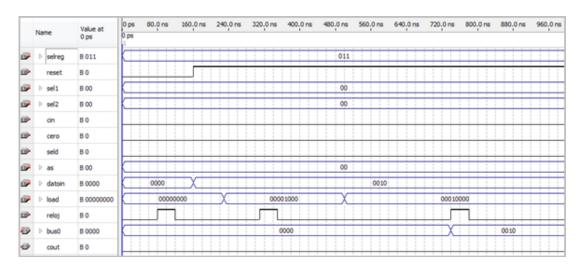

La Figura 6 muestra la simulación de una prueba sencilla del funcionamiento de la descripción de la arquitectura de la computadora básica en donde se inicia con un reset a todos los componentes, se selecciona el componente el cual ha de aparecer en sistema de bus, acontinuación se proporciona un dato de entrada el cual es cargado en el registro de entrada y se transfiere a través de la unidad aritmética lógica y de corrimiento para que finalmenente quede cargado en el registro acumulador.

Figura 6. Transferencia de un dato en la computadora

# DISCUSIÓN DE RESULTADOS

Se probaron diferentes ejemplos de diseño para las materias del área de sistemas digitales de la carrera de Ing. en Sistemas Computacionales. En la Tabla 1 se muestran los temas en los se puede aplicar CAD como apoyo a la enseñanza, también se indica el porcentaje de cobertura del tema empleando esta técnica.

| Tabla 1. A   | plicación o  | de diseño  | asistido | por com   | putadora | por materia  |

|--------------|--------------|------------|----------|-----------|----------|--------------|

| I WOIW IT II | piicacioii ( | ac albeito | abibliao | POI COIII | pulluoiu | poi illuttia |

| MATERIA                |   | TEMAS                                     | APLICACIÓN<br>DE DAC |

|------------------------|---|-------------------------------------------|----------------------|

| Principios Eléctricos  | y | 1. Electrónica analógica                  | -                    |

| Aplicaciones Digitales |   | 2. Electrónica Digital                    | 100 %                |

|                        |   | 3. Convertidores                          | -                    |

|                        |   | 4. Lenguajes HDL                          | 100 %                |

| Arquitectura de        |   | 1. Arquitecturas de cómputo               | 100 %                |

| Computadoras           |   | 2. Estructura y funcionamiento de la CPU  | 100%                 |

| _                      |   | 3. Selección de componentes para ensamble |                      |

|                        |   | de equipo de cómputo                      | -                    |

|                        |   | 4. Procesamiento paralelo                 | -                    |

| Sistemas Programables  |   | 1. Sensores                               | -                    |

|                        |   | 2. Actuadores                             | -                    |

|                        |   | 3. Microcontroladores                     | 100 %                |

|                        |   | 4. Programación de microcontroladores     | 100 %                |

|                        |   | 5. Puertos y buses de comunicación para   | -                    |

|                        |   | microcontroladores.                       |                      |

|                        |   | 6. interfaces                             | -                    |

En base a un trabajo desarrollado mediante el empleo de CAD se tuvo la oportunidad participar en el 1er Encuentro de Jóvenes Investigadores en la presentación oral de los estudiantes Joel Alberto Benito García y José Luis Andrade García del ITESI con el trabajo "Implementación de transferencia de registros y microoperaciones para arquitectura de computadoras empleando Quartus II y Cyclone II". El evento se celebró en la ciudad de Guanajuato, Gto. el 28 y 29 de noviembre 2013 en las instalaciones de la Universidad de

Guanajuato. En la Figura 7 se muestra la presentación oral en el encuentro de jóvenes investigadores.

Figura 7. 1er. Encuentro de Jóvenes Investigadores

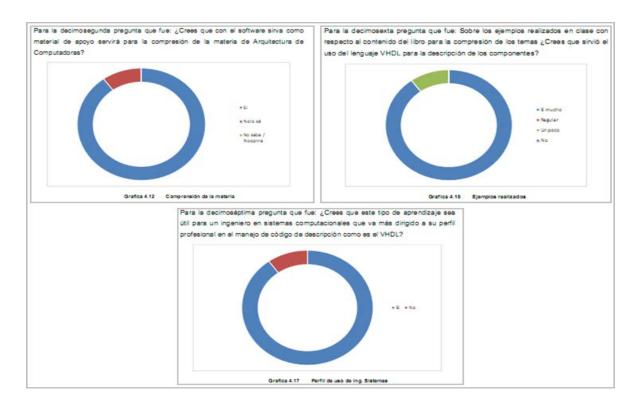

Para conocer el grado de aceptación del uso de CAD para un determinado curso por parte de los alumnos, se aplicó una encuesta al grupo de estudiantes del curso Arquitectura de Computadoras del semestre Agosto-Diciembre de 2013, en donde 9 de 10 estudiantes manifestaron que creen que el software servirá de apoyo para la comprensión de la materia, que el lenguaje sirvió para describir los componentes y que este tipo de aprendizaje será útil para su perfil profesional. En la Figura 8 se muestra las preguntas más relevantes.

Figura 8. Encuesta a alumnos

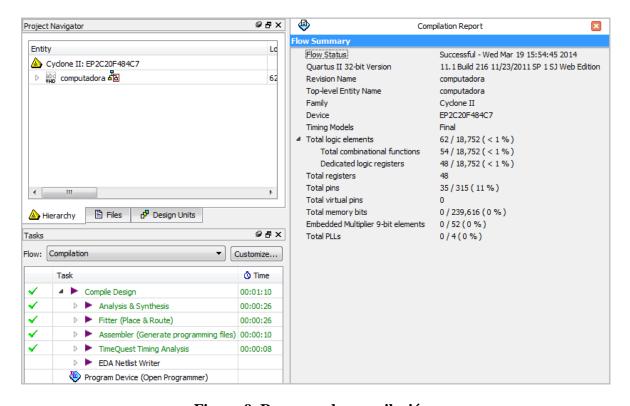

En los diferentes ejemplos de diseño realizados, se debe poner atención en que la compilación se realice de forma exitosa y que los componentes descritos puedan ser realizables físicamente en la tarjeta. En la Figura 9 se muestra el resumen del informe de la compilación de uno de los ejemplos más complicados que pueden cubrirse en un curso introductorio de Arquitectura de Computadoras, la descripción de la computadora básica. Como puede observarse el porcentaje de utilización de la tarjeta es menor del 1% de su capacidad física.

En diferentes trabajos de investigación se ha publicado el uso del hardware dedicado y las aplicaciones de los dispositivos programables de alto desempeño como las FPGAs. Por ejemplo considere lo siguiente: "Debido a la naturaleza discreta de secuencias de péptidos, el cálculo de las propiedades físico-químicas se considera un problema de computación de alto rendimiento. Una solución competitiva para esta clase de problemas es la de insertar algoritmos en hardware dedicado (FPGA)" (Polanco, Nuño, Arias-Estrada, & del Rio, 2011). Por lo que se propone ampliar el panorama para los estudiantes en las aplicaciones de CAD en temas avanzados de arquitectura de computadoras o aplicaciones de cómputo de alto desempeño en áreas como investigación biológica.

Figura 9. Resumen de compilación

Con el objeto de promover el uso en los estudiantes de la carera de Ing. en Sistemas Computacionales la técnica CAD se impartió el taller "Programación de Hardware" durante la Semana Tecnológica 2013 en el marco de la XX Semana Nacional de Ciencia y Tecnología celebrado el 22 y 24 de octubre de 2013 en el ITESI. En la Figura 10 se muestra una sesión del taller.

Figura 10. Taller de programación de Hardware

### **CONCLUSIONES**

Mediante la técnica CAD es posible cubrir los temas de sistemas digitales de las materias de la carrera de Ingeniería en Sistemas Computacionales. Facilita el proceso de enseñanza ya que permite abordar los temas de forma gradual iniciando desde los componentes más sencillos los cuales se pueden probar por separado e integrarlos posteriormente a un proyecto más complejo. El uso de esta técnica es viable ya que se emplea una versión software accesible para los estudiantes, la tarjeta es de bajo costo y no se requiere equipamiento de laboratorio adicional. El grado de aceptación por parte de los estudiantes es bastante bueno. Se puede observar que la capacidad empleada de la tarjeta es mínima por lo que se puede proponer ampliar el panorama para el estudio de aplicaciones de cómputo científico.

Con la realización de este proyecto se pretende adquirir conocimientos de la técnica de diseño asistido por computadora por parte de la comunidad estudiantil y académica del ITESI para incorporarla en la dinámica de los cursos del área de sistemas digitales y servir como base para el planteamiento de proyectos más robustos donde se requiera el cómputo científico basado en hardware

### BIBLIOGRAFÍA

Altera Corporation. (2006). Quartus II Introduction for VHDL Users. Altera Corporation.

Mano, M. M. (1994). Arquitectura de Computadoras. México: Prentice Hall.

Maxinez, D. G., & Alcalá, J. (2002). VHDL El arte de programar sistemas digitales. México: Cecsa.

Pardo, F., & Boluda, J. A. (1999). VHDL Lenguaje para síntesis y modelado de circuitos. México: Alfaomega.

Polanco, C., Nuño, M. A., Arias-Estrada, M., & del Rio, G. (2011). An FPGA

Implementation to Detect Selective Cationic Antibacterial Peptides. *PlosOne* .

Romero, R. d. (2007). *Electrónica Digital y Lógica Programable*. Mexico: Universidad de Guanajuato.